스마트폰, 인공지능 메인 칩으로 들어가는 전기의 전압을 일정하게 잡아주고, 잡음을 걸러내는 초소형 반도체가 개발됐다. 전력 관리 성능은 세계 최고 수준을 기록했으며 크기는 더 작아졌다. 연산 코어가 쉴 새 없이 작동해 전압 변동이 큰 AI 반도체, 잡음에 민감한 6G 통신 칩 등 고집적 시스템 온 칩(SoC) 개발에 도움이 될 것으로 기대된다.

울산과학기술원(UNIST) 전기전자공학과 윤희인 교수팀은 초소형 하이브리드 전력관리 반도체 LDO를 개발했다고 29일 밝혔다. LDO는 메인 반도체로 공급되는 전원을 관리하는 반도체다. 가령 스마트폰 게임 앱을 갑자기 켜거나 끄면 전류 사용이 급격히 변하면서 전압도 들쭉날쭉해지는데, 이러한 전압 출렁임을 잡아내고 직류 전압에 섞여 들어온 교류 성분의 잡음까지 걸러내는 역할이다.

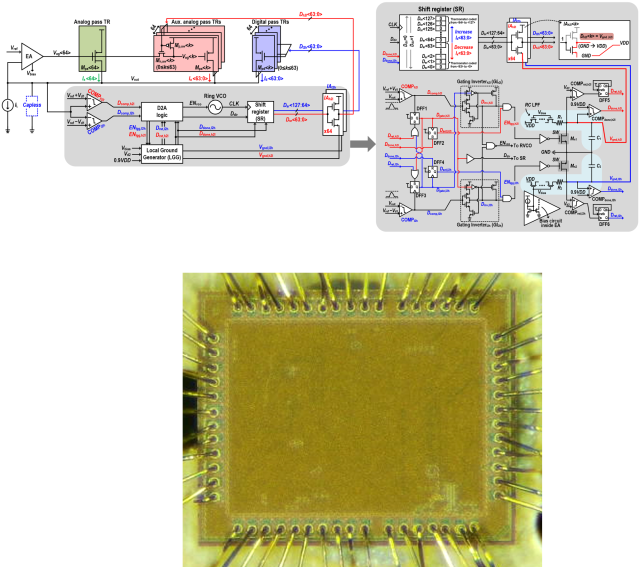

개발된 LDO는 아날로그 회로 기반에 디지털 회로의 장점을 조합한 하이브리드 구조로, 디지털 회로의 우수한 전압 안정화 성능과 아날로그 회로의 잡음 억제 성능을 모두 갖췄다.

실제 이 LDO는 99㎃(밀리암페어)의 전류 변화가 있었을 때도 출력 전압의 출렁임을 54㎷(밀리볼트) 수준으로 억제했고, 667나노초 만에 전압을 원래대로 복귀시켰다. 잡음 억제 성능(PSRR)도 –53.7㏈(100㎃ 부하, 10㎑ 기준)를 기록했다. 10㎑ 주파수의 잡음이 섞여 들어왔다고 할 때, 99.8%를 걸러낼 수 있다는 의미다.

또 커패시터를 없애 기존 하이브리드 구조 대비 크기를 줄였다. 28나노미터 CMOS 공정으로 제작했을 때 크기는 0.032㎟에 불과하다. 크기를 줄이면 칩에서 더 많은 LDO를 넣을 수 있어, 시스템 온 칩(SoC)과 같이 여러 기능 블록이 집적된 고성능 칩을 만드는데 더 적합하다.

제1저자인 안창민 연구원은 “일반적인 하이브리드 구조는 디지털에서 아날로그로의 전환이 매끄럽지 않아 완충 장치 역할을 하는 커패시터가 회로 구조에 들어가는데, 끊김 없는 디지털-아날로그 전환(D2A-TF)’과 ‘LGG(Local Ground Generator)’라는 새로운 회로 설계 방식으로 이를 해결했다”고 설명했다.

이 LDO는 전류가 급격하게 변하는 이벤트가 있을 때만 디지털 회로가 켜지도록 설계돼 대기 전력 소모도 적다. 대기 전류와 전압 안정화 속도, 잡음억제 능력을 종합적으로 평가하는 성능 지표(FoM)에서 0.029㎰라는 세계 최고 수준을 기록했다.

윤희인 교수는 “전압 안정화 능력과 잡음 제거 성능이 모두 뛰어난 초소형 저전력 회로로, AI 반도체, 6G 통신칩 등 시스템온칩 개발 등 폭넓게 쓰일 수 있을 것”이라고 기대했다.

이번 연구는 IEEE 반도체 회로 공학회에서 발행하는 회로설계 분야 저명 학술지인 ‘저널 오브 솔리드 스테이트 서킷(Journal of Solid-State Circuits)’에 9월 3일에 게재됐다. 연구 수행은 과학기술정보통신부, 반도체설계교육센터, 과학기술정보통신부 정보통신기획평가원(IITP)의 지역지능화혁신인재양성사업의 지원으로 이뤄졌다.